ਛੋਟੇ ਵੋਲਟੇਜ MOSFET ਚੋਣ ਦਾ ਇੱਕ ਬਹੁਤ ਹੀ ਮਹੱਤਵਪੂਰਨ ਹਿੱਸਾ ਹੈMOSFETਚੋਣ ਚੰਗੀ ਨਹੀਂ ਹੈ, ਪੂਰੇ ਸਰਕਟ ਦੀ ਕੁਸ਼ਲਤਾ ਅਤੇ ਲਾਗਤ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰ ਸਕਦੀ ਹੈ, ਪਰ ਇਹ ਇੰਜੀਨੀਅਰਾਂ ਲਈ ਬਹੁਤ ਮੁਸ਼ਕਲ ਵੀ ਲਿਆਏਗੀ, ਕਿ MOSFET ਦੀ ਸਹੀ ਚੋਣ ਕਿਵੇਂ ਕਰੀਏ?

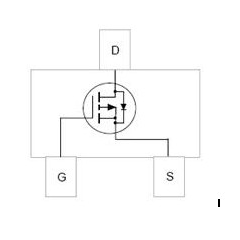

N-ਚੈਨਲ ਜਾਂ P-ਚੈਨਲ ਦੀ ਚੋਣ ਕਰਨਾ ਕਿਸੇ ਡਿਜ਼ਾਈਨ ਲਈ ਸਹੀ ਯੰਤਰ ਦੀ ਚੋਣ ਕਰਨ ਦਾ ਪਹਿਲਾ ਕਦਮ ਇਹ ਫੈਸਲਾ ਕਰਨਾ ਹੈ ਕਿ ਕੀ ਇੱਕ N-ਚੈਨਲ ਜਾਂ P-ਚੈਨਲ MOSFET ਦੀ ਵਰਤੋਂ ਕਰਨੀ ਹੈ ਇੱਕ ਆਮ ਪਾਵਰ ਐਪਲੀਕੇਸ਼ਨ ਵਿੱਚ, ਇੱਕ MOSFET ਇੱਕ ਘੱਟ-ਵੋਲਟੇਜ ਸਾਈਡ ਸਵਿੱਚ ਬਣਾਉਂਦਾ ਹੈ ਜਦੋਂ MOSFET ਜ਼ਮੀਨੀ ਹੈ ਅਤੇ ਲੋਡ ਟਰੰਕ ਵੋਲਟੇਜ ਨਾਲ ਜੁੜਿਆ ਹੋਇਆ ਹੈ। ਇੱਕ ਘੱਟ ਵੋਲਟੇਜ ਵਾਲੇ ਪਾਸੇ ਦੇ ਸਵਿੱਚ ਵਿੱਚ, ਇੱਕ N-ਚੈਨਲ MOSFET ਦੀ ਵਰਤੋਂ ਡਿਵਾਈਸ ਨੂੰ ਬੰਦ ਕਰਨ ਜਾਂ ਚਾਲੂ ਕਰਨ ਲਈ ਲੋੜੀਂਦੀ ਵੋਲਟੇਜ ਦੇ ਕਾਰਨ ਕੀਤੀ ਜਾਣੀ ਚਾਹੀਦੀ ਹੈ।

ਜਦੋਂ MOSFET ਨੂੰ ਬੱਸ ਨਾਲ ਜੋੜਿਆ ਜਾਂਦਾ ਹੈ ਅਤੇ ਲੋਡ ਨੂੰ ਗਰਾਊਂਡ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਹਾਈ ਵੋਲਟੇਜ ਵਾਲੇ ਪਾਸੇ ਵਾਲੇ ਸਵਿੱਚ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਣੀ ਹੈ। ਪੀ-ਚੈਨਲ MOSFETs ਦੀ ਵਰਤੋਂ ਆਮ ਤੌਰ 'ਤੇ ਇਸ ਟੋਪੋਲੋਜੀ ਵਿੱਚ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਮੁੜ ਵੋਲਟੇਜ ਡਰਾਈਵ ਦੇ ਵਿਚਾਰਾਂ ਲਈ। ਮੌਜੂਦਾ ਰੇਟਿੰਗ ਨਿਰਧਾਰਤ ਕਰੋ। MOSFET ਦੀ ਮੌਜੂਦਾ ਰੇਟਿੰਗ ਚੁਣੋ। ਸਰਕਟ ਬਣਤਰ 'ਤੇ ਨਿਰਭਰ ਕਰਦੇ ਹੋਏ, ਇਹ ਮੌਜੂਦਾ ਰੇਟਿੰਗ ਵੱਧ ਤੋਂ ਵੱਧ ਕਰੰਟ ਹੋਣੀ ਚਾਹੀਦੀ ਹੈ ਜਿਸਦਾ ਲੋਡ ਹਰ ਹਾਲਤ ਵਿੱਚ ਬਰਦਾਸ਼ਤ ਕਰ ਸਕਦਾ ਹੈ।

ਵੋਲਟੇਜ ਦੇ ਮਾਮਲੇ ਦੇ ਸਮਾਨ, ਡਿਜ਼ਾਈਨਰ ਨੂੰ ਇਹ ਯਕੀਨੀ ਬਣਾਉਣਾ ਚਾਹੀਦਾ ਹੈ ਕਿ ਚੁਣਿਆ ਗਿਆ ਹੈMOSFETਇਸ ਮੌਜੂਦਾ ਰੇਟਿੰਗ ਦਾ ਸਾਮ੍ਹਣਾ ਕਰ ਸਕਦਾ ਹੈ, ਭਾਵੇਂ ਸਿਸਟਮ ਸਪਾਈਕ ਕਰੰਟ ਤਿਆਰ ਕਰ ਰਿਹਾ ਹੋਵੇ। ਵਿਚਾਰਨ ਲਈ ਦੋ ਮੌਜੂਦਾ ਮਾਮਲੇ ਨਿਰੰਤਰ ਮੋਡ ਅਤੇ ਪਲਸ ਸਪਾਈਕ ਹਨ। ਨਿਰੰਤਰ ਸੰਚਾਲਨ ਮੋਡ ਵਿੱਚ, MOSFET ਸਥਿਰ ਸਥਿਤੀ ਵਿੱਚ ਹੁੰਦਾ ਹੈ, ਜਦੋਂ ਕਰੰਟ ਲਗਾਤਾਰ ਡਿਵਾਈਸ ਵਿੱਚੋਂ ਲੰਘਦਾ ਹੈ।

ਪਲਸ ਸਪਾਈਕਸ ਉਦੋਂ ਹੁੰਦੇ ਹਨ ਜਦੋਂ ਯੰਤਰ ਰਾਹੀਂ ਵਹਿਣ ਵਾਲੇ ਵੱਡੇ ਵਾਧੇ (ਜਾਂ ਕਰੰਟ ਦੇ ਸਪਾਈਕਸ) ਹੁੰਦੇ ਹਨ। ਇੱਕ ਵਾਰ ਜਦੋਂ ਇਹਨਾਂ ਸ਼ਰਤਾਂ ਅਧੀਨ ਅਧਿਕਤਮ ਕਰੰਟ ਨਿਰਧਾਰਤ ਕੀਤਾ ਗਿਆ ਹੈ, ਤਾਂ ਇਹ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਇੱਕ ਉਪਕਰਣ ਦੀ ਚੋਣ ਕਰਨ ਦਾ ਮਾਮਲਾ ਹੈ ਜੋ ਇਸ ਅਧਿਕਤਮ ਕਰੰਟ ਦਾ ਸਾਮ੍ਹਣਾ ਕਰ ਸਕਦਾ ਹੈ। ਥਰਮਲ ਲੋੜਾਂ ਨੂੰ ਨਿਰਧਾਰਤ ਕਰਨਾ ਇੱਕ MOSFET ਦੀ ਚੋਣ ਕਰਨ ਲਈ ਸਿਸਟਮ ਦੀਆਂ ਥਰਮਲ ਲੋੜਾਂ ਦੀ ਗਣਨਾ ਕਰਨ ਦੀ ਵੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਡਿਜ਼ਾਈਨਰ ਨੂੰ ਦੋ ਵੱਖ-ਵੱਖ ਦ੍ਰਿਸ਼ਾਂ 'ਤੇ ਵਿਚਾਰ ਕਰਨਾ ਚਾਹੀਦਾ ਹੈ, ਸਭ ਤੋਂ ਮਾੜਾ ਕੇਸ ਅਤੇ ਸੱਚਾ ਕੇਸ। ਇਹ ਸਿਫ਼ਾਰਸ਼ ਕੀਤੀ ਜਾਂਦੀ ਹੈ ਕਿ ਸਭ ਤੋਂ ਮਾੜੇ-ਕੇਸ ਗਣਨਾ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਵੇ ਕਿਉਂਕਿ ਇਹ ਸੁਰੱਖਿਆ ਦਾ ਇੱਕ ਵੱਡਾ ਮਾਰਜਿਨ ਪ੍ਰਦਾਨ ਕਰਦਾ ਹੈ ਅਤੇ ਇਹ ਯਕੀਨੀ ਬਣਾਉਂਦਾ ਹੈ ਕਿ ਸਿਸਟਮ ਫੇਲ ਨਹੀਂ ਹੋਵੇਗਾ। MOSFET ਡੇਟਾ ਸ਼ੀਟ 'ਤੇ ਜਾਣੂ ਹੋਣ ਲਈ ਕੁਝ ਮਾਪ ਵੀ ਹਨ; ਜਿਵੇਂ ਕਿ ਪੈਕੇਜ ਡਿਵਾਈਸ ਦੇ ਸੈਮੀਕੰਡਕਟਰ ਜੰਕਸ਼ਨ ਅਤੇ ਵਾਤਾਵਰਣ ਵਿਚਕਾਰ ਥਰਮਲ ਪ੍ਰਤੀਰੋਧ, ਅਤੇ ਵੱਧ ਤੋਂ ਵੱਧ ਜੰਕਸ਼ਨ ਤਾਪਮਾਨ। ਪ੍ਰਦਰਸ਼ਨ ਨੂੰ ਬਦਲਣ ਦਾ ਫੈਸਲਾ ਕਰਦੇ ਹੋਏ, ਇੱਕ MOSFET ਦੀ ਚੋਣ ਕਰਨ ਦਾ ਅੰਤਮ ਕਦਮ ਹੈ ਸਵਿਚਿੰਗ ਪ੍ਰਦਰਸ਼ਨ 'ਤੇ ਫੈਸਲਾ ਕਰਨਾMOSFET.

ਬਹੁਤ ਸਾਰੇ ਮਾਪਦੰਡ ਹਨ ਜੋ ਸਵਿਚਿੰਗ ਪ੍ਰਦਰਸ਼ਨ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰਦੇ ਹਨ, ਪਰ ਸਭ ਤੋਂ ਮਹੱਤਵਪੂਰਨ ਹਨ ਗੇਟ/ਡਰੇਨ, ਗੇਟ/ਸਰੋਤ, ਅਤੇ ਡਰੇਨ/ਸਰੋਤ ਸਮਰੱਥਾ। ਇਹ ਸਮਰੱਥਾ ਡਿਵਾਈਸ ਵਿੱਚ ਸਵਿਚਿੰਗ ਨੁਕਸਾਨ ਪੈਦਾ ਕਰਦੇ ਹਨ ਕਿਉਂਕਿ ਉਹਨਾਂ ਨੂੰ ਹਰੇਕ ਸਵਿਚਿੰਗ ਦੌਰਾਨ ਚਾਰਜ ਕਰਨਾ ਪੈਂਦਾ ਹੈ। ਇਸ ਲਈ MOSFET ਦੀ ਸਵਿਚਿੰਗ ਸਪੀਡ ਘੱਟ ਜਾਂਦੀ ਹੈ ਅਤੇ ਡਿਵਾਈਸ ਦੀ ਕੁਸ਼ਲਤਾ ਘੱਟ ਜਾਂਦੀ ਹੈ। ਸਵਿਚਿੰਗ ਦੌਰਾਨ ਡਿਵਾਈਸ ਦੇ ਕੁੱਲ ਨੁਕਸਾਨ ਦੀ ਗਣਨਾ ਕਰਨ ਲਈ, ਡਿਜ਼ਾਈਨਰ ਨੂੰ ਟਰਨ-ਆਨ ਨੁਕਸਾਨ (ਈਓਨ) ਅਤੇ ਟਰਨ-ਆਫ ਨੁਕਸਾਨ ਦੀ ਗਣਨਾ ਕਰਨੀ ਚਾਹੀਦੀ ਹੈ।

ਜਦੋਂ vGS ਦਾ ਮੁੱਲ ਛੋਟਾ ਹੁੰਦਾ ਹੈ, ਇਲੈਕਟ੍ਰੌਨਾਂ ਨੂੰ ਜਜ਼ਬ ਕਰਨ ਦੀ ਸਮਰੱਥਾ ਮਜ਼ਬੂਤ ਨਹੀਂ ਹੁੰਦੀ ਹੈ, ਲੀਕੇਜ - ਸਰੋਤ ਅਜੇ ਵੀ ਕੋਈ ਸੰਚਾਲਕ ਚੈਨਲ ਪੇਸ਼ ਨਹੀਂ ਕਰਦਾ, vGS ਵਾਧਾ, ਵਾਧੇ 'ਤੇ ਇਲੈਕਟ੍ਰੌਨਾਂ ਦੀ P ਘਟਾਓਣਾ ਬਾਹਰੀ ਸਤਹ ਪਰਤ ਵਿੱਚ ਲੀਨ ਹੋ ਜਾਂਦਾ ਹੈ, ਜਦੋਂ vGS ਪਹੁੰਚਦਾ ਹੈ a ਨਿਸ਼ਚਿਤ ਮੁੱਲ, ਪੀ ਸਬਸਟਰੇਟ ਦਿੱਖ ਦੇ ਨੇੜੇ ਗੇਟ ਵਿੱਚ ਇਹ ਇਲੈਕਟ੍ਰੌਨ N- ਕਿਸਮ ਦੀ ਇੱਕ ਪਤਲੀ ਪਰਤ ਬਣਾਉਂਦੇ ਹਨ, ਅਤੇ ਦੋ N + ਜ਼ੋਨ ਦੇ ਨਾਲ ਜੁੜੇ ਹੁੰਦੇ ਹਨ vGS ਇੱਕ ਨਿਸ਼ਚਿਤ ਮੁੱਲ ਤੱਕ ਪਹੁੰਚਦਾ ਹੈ, P ਸਬਸਟਰੇਟ ਦਿੱਖ ਦੇ ਨੇੜੇ ਗੇਟ ਵਿੱਚ ਇਹ ਇਲੈਕਟ੍ਰੌਨ ਇੱਕ N- ਕਿਸਮ ਦੀ ਪਤਲੀ ਪਰਤ ਦਾ ਗਠਨ ਕਰਨਗੇ, ਅਤੇ ਦੋ N + ਖੇਤਰ ਨਾਲ ਜੁੜੇ ਹੋਏ ਹਨ, ਡਰੇਨ ਵਿੱਚ - ਸਰੋਤ N- ਕਿਸਮ ਦੇ ਸੰਚਾਲਕ ਚੈਨਲ ਦਾ ਗਠਨ ਕਰਦੇ ਹਨ, ਇਸਦੀ ਸੰਚਾਲਕ ਕਿਸਮ ਅਤੇ ਪੀ ਸਬਸਟਰੇਟ ਦੇ ਉਲਟ, ਐਂਟੀ-ਟਾਈਪ ਲੇਅਰ ਦਾ ਗਠਨ ਕਰਦਾ ਹੈ। vGS ਵੱਡਾ ਹੁੰਦਾ ਹੈ, ਸੈਮੀਕੰਡਕਟਰ ਦਿੱਖ ਦੀ ਭੂਮਿਕਾ ਇਲੈਕਟ੍ਰਿਕ ਫੀਲਡ ਦੀ ਮਜ਼ਬੂਤੀ, P ਸਬਸਟਰੇਟ ਦੇ ਬਾਹਰਲੇ ਹਿੱਸੇ ਵਿੱਚ ਇਲੈਕਟ੍ਰੌਨਾਂ ਦੀ ਸਮਾਈ ਹੁੰਦੀ ਹੈ, ਜਿੰਨਾ ਜ਼ਿਆਦਾ ਸੰਚਾਲਕ ਚੈਨਲ ਮੋਟਾ ਹੁੰਦਾ ਹੈ, ਚੈਨਲ ਪ੍ਰਤੀਰੋਧ ਘੱਟ ਹੁੰਦਾ ਹੈ। ਯਾਨੀ, VGS < VT ਵਿੱਚ N-ਚੈਨਲ MOSFET, ਇੱਕ ਕੰਡਕਟਿਵ ਚੈਨਲ ਨਹੀਂ ਬਣਾ ਸਕਦਾ, ਟਿਊਬ ਕੱਟ-ਆਫ ਅਵਸਥਾ ਵਿੱਚ ਹੈ। ਜਿੰਨਾ ਚਿਰ vGS ≥ VT, ਸਿਰਫ਼ ਉਦੋਂ ਜਦੋਂ ਚੈਨਲ ਰਚਨਾ। ਚੈਨਲ ਦੇ ਗਠਨ ਤੋਂ ਬਾਅਦ, ਡਰੇਨ - ਸਰੋਤ ਦੇ ਵਿਚਕਾਰ ਇੱਕ ਫਾਰਵਰਡ ਵੋਲਟੇਜ vDS ਜੋੜ ਕੇ ਇੱਕ ਡਰੇਨ ਕਰੰਟ ਪੈਦਾ ਹੁੰਦਾ ਹੈ।

ਪਰ Vgs ਲਗਾਤਾਰ ਵਧਦਾ ਜਾ ਰਿਹਾ ਹੈ, ਮੰਨ ਲਓ ਕਿ IRFPS40N60KVgs = 100V ਜਦੋਂ Vds = 0 ਅਤੇ Vds = 400V, ਦੋ ਸਥਿਤੀਆਂ, ਟਿਊਬ ਫੰਕਸ਼ਨ ਕੀ ਪ੍ਰਭਾਵ ਲਿਆਉਣ ਲਈ, ਜੇਕਰ ਸਾੜ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਪ੍ਰਕਿਰਿਆ ਦਾ ਕਾਰਨ ਅਤੇ ਅੰਦਰੂਨੀ ਵਿਧੀ ਇਹ ਹੈ ਕਿ ਕਿਵੇਂ Vgs ਨੂੰ ਵਧਾਉਣਾ ਘਟੇਗਾ। Rds (ਚਾਲੂ) ਸਵਿਚਿੰਗ ਘਾਟੇ ਨੂੰ ਘਟਾਉਂਦਾ ਹੈ, ਪਰ ਉਸੇ ਸਮੇਂ Qg ਵਧਾਏਗਾ, ਤਾਂ ਜੋ ਚਾਲੂ ਹੋਣ ਦਾ ਨੁਕਸਾਨ ਹੋ ਜਾਵੇ ਵੱਡਾ, Vgg ਤੋਂ Cgs ਚਾਰਜਿੰਗ ਅਤੇ ਰਾਈਜ਼ ਦੁਆਰਾ MOSFET GS ਵੋਲਟੇਜ ਦੀ ਕੁਸ਼ਲਤਾ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰਦੇ ਹੋਏ, ਰੱਖ-ਰਖਾਅ ਵੋਲਟੇਜ Vth 'ਤੇ ਪਹੁੰਚਿਆ, MOSFET ਸਟਾਰਟ ਕੰਡਕਟਿਵ; MOSFET DS ਮੌਜੂਦਾ ਵਾਧਾ, DS capacitance ਅਤੇ ਡਿਸਚਾਰਜ ਦੇ ਡਿਸਚਾਰਜ ਦੇ ਕਾਰਨ ਅੰਤਰਾਲ ਵਿੱਚ Millier capacitance, GS capacitance ਚਾਰਜਿੰਗ ਦਾ ਜ਼ਿਆਦਾ ਪ੍ਰਭਾਵ ਨਹੀਂ ਹੁੰਦਾ; Qg = Cgs * Vgs, ਪਰ ਚਾਰਜ ਬਣਨਾ ਜਾਰੀ ਰਹੇਗਾ।

MOSFET ਦਾ DS ਵੋਲਟੇਜ Vgs ਦੇ ਸਮਾਨ ਵੋਲਟੇਜ ਵਿੱਚ ਆ ਜਾਂਦਾ ਹੈ, ਮਿਲੀਅਰ ਕੈਪੈਸੀਟੈਂਸ ਬਹੁਤ ਵਧ ਜਾਂਦੀ ਹੈ, ਬਾਹਰੀ ਡਰਾਈਵ ਵੋਲਟੇਜ ਮਿਲੀਅਰ ਕੈਪੈਸੀਟੈਂਸ ਨੂੰ ਚਾਰਜ ਕਰਨਾ ਬੰਦ ਕਰ ਦਿੰਦੀ ਹੈ, GS ਕੈਪੈਸੀਟੈਂਸ ਦੀ ਵੋਲਟੇਜ ਬਦਲਦੀ ਰਹਿੰਦੀ ਹੈ, ਮਿਲੀਅਰ ਕੈਪੈਸੀਟੈਂਸ ਉੱਤੇ ਵੋਲਟੇਜ ਵਧਦੀ ਹੈ, ਜਦੋਂ ਕਿ ਡੀ.ਐਸ. ਦੀ ਸਮਰੱਥਾ ਘਟਦੀ ਰਹਿੰਦੀ ਹੈ; MOSFET ਦਾ DS ਵੋਲਟੇਜ ਸੰਤ੍ਰਿਪਤ ਸੰਚਾਲਨ 'ਤੇ ਵੋਲਟੇਜ ਤੱਕ ਘੱਟ ਜਾਂਦਾ ਹੈ, ਮਿਲੀਅਰ ਕੈਪੈਸੀਟੈਂਸ ਛੋਟਾ ਹੋ ਜਾਂਦਾ ਹੈ MOSFET ਦਾ DS ਵੋਲਟੇਜ ਸੰਤ੍ਰਿਪਤ ਸੰਚਾਲਨ 'ਤੇ ਵੋਲਟੇਜ ਤੱਕ ਘੱਟ ਜਾਂਦਾ ਹੈ, ਮਿਲੀਅਰ ਕੈਪੈਸੀਟੈਂਸ ਛੋਟਾ ਹੋ ਜਾਂਦਾ ਹੈ ਅਤੇ ਬਾਹਰੀ ਡਰਾਈਵ ਦੁਆਰਾ GS ਕੈਪੈਸੀਟੈਂਸ ਦੇ ਨਾਲ ਚਾਰਜ ਕੀਤਾ ਜਾਂਦਾ ਹੈ ਵੋਲਟੇਜ, ਅਤੇ GS ਕੈਪੈਸੀਟੈਂਸ 'ਤੇ ਵੋਲਟੇਜ ਵਧਦਾ ਹੈ; ਵੋਲਟੇਜ ਮਾਪਣ ਵਾਲੇ ਚੈਨਲ ਘਰੇਲੂ 3D01, 4D01, ਅਤੇ ਨਿਸਾਨ ਦੀ 3SK ਸੀਰੀਜ਼ ਹਨ।

ਜੀ-ਪੋਲ (ਗੇਟ) ਨਿਰਧਾਰਨ: ਮਲਟੀਮੀਟਰ ਦੇ ਡਾਇਓਡ ਗੇਅਰ ਦੀ ਵਰਤੋਂ ਕਰੋ। ਜੇਕਰ ਸਕਾਰਾਤਮਕ ਅਤੇ ਨਕਾਰਾਤਮਕ ਵੋਲਟੇਜ ਡ੍ਰੌਪ ਦੇ ਵਿਚਕਾਰ ਇੱਕ ਪੈਰ ਅਤੇ ਦੂਜੇ ਦੋ ਪੈਰ 2V ਤੋਂ ਵੱਧ ਹਨ, ਯਾਨੀ ਡਿਸਪਲੇਅ "1", ਤਾਂ ਇਹ ਫੁੱਟ ਗੇਟ G ਹੈ। ਅਤੇ ਫਿਰ ਬਾਕੀ ਦੇ ਦੋ ਪੈਰਾਂ ਨੂੰ ਮਾਪਣ ਲਈ ਪੈੱਨ ਨੂੰ ਬਦਲੋ, ਵੋਲਟੇਜ ਡਰਾਪ ਉਸ ਸਮੇਂ ਛੋਟਾ ਹੁੰਦਾ ਹੈ, ਕਾਲਾ ਪੈੱਨ ਡੀ-ਪੋਲ (ਡਰੇਨ) ਨਾਲ ਜੁੜਿਆ ਹੁੰਦਾ ਹੈ, ਲਾਲ ਪੈੱਨ ਐਸ-ਪੋਲ (ਸਰੋਤ) ਨਾਲ ਜੁੜਿਆ ਹੁੰਦਾ ਹੈ।